SDRAM文件結(jié)構(gòu)存儲(chǔ)控制的FPGA實(shí)現(xiàn)與數(shù)據(jù)處理存儲(chǔ)支持服務(wù)

在現(xiàn)代數(shù)字系統(tǒng)中,SDRAM(同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器)因其高容量、高速度和低成本的優(yōu)勢,被廣泛應(yīng)用于數(shù)據(jù)緩存和大容量存儲(chǔ)場景。SDRAM的復(fù)雜時(shí)序控制和文件結(jié)構(gòu)管理對(duì)硬件實(shí)現(xiàn)提出了較高要求。FPGA(現(xiàn)場可編程門陣列)以其靈活的可編程性和并行處理能力,成為實(shí)現(xiàn)SDRAM存儲(chǔ)控制的理想平臺(tái)。本文將分析SDRAM文件結(jié)構(gòu)存儲(chǔ)控制的FPGA實(shí)現(xiàn),并探討其數(shù)據(jù)處理和存儲(chǔ)支持服務(wù)的關(guān)鍵技術(shù)。

一、SDRAM文件結(jié)構(gòu)存儲(chǔ)控制的FPGA實(shí)現(xiàn)

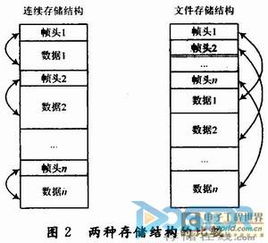

SDRAM存儲(chǔ)控制的核心在于對(duì)讀寫時(shí)序、地址映射和刷新機(jī)制的管理。在FPGA中,通常通過狀態(tài)機(jī)設(shè)計(jì)來實(shí)現(xiàn)這些功能。需要設(shè)計(jì)初始化模塊,負(fù)責(zé)在系統(tǒng)上電后對(duì)SDRAM進(jìn)行模式寄存器設(shè)置,包括突發(fā)長度、潛伏期等參數(shù)。讀寫控制模塊需處理命令序列,如激活行、讀/寫列和預(yù)充電操作,確保數(shù)據(jù)在正確的時(shí)鐘沿被采樣。對(duì)于文件結(jié)構(gòu)存儲(chǔ),F(xiàn)PGA需實(shí)現(xiàn)邏輯地址到物理地址的映射,支持文件系統(tǒng)的塊管理,例如FAT或自定義格式,以優(yōu)化存儲(chǔ)空間利用。FPGA還可以集成ECC(錯(cuò)誤校正碼)模塊,提升數(shù)據(jù)可靠性。通過硬件描述語言(如Verilog或VHDL)編碼,這些模塊可以并行運(yùn)行,實(shí)現(xiàn)低延遲和高吞吐量的存儲(chǔ)控制。

二、數(shù)據(jù)處理支持服務(wù)

在SDRAM存儲(chǔ)控制的基礎(chǔ)上,F(xiàn)PGA能夠提供高效的數(shù)據(jù)處理支持服務(wù)。這包括數(shù)據(jù)預(yù)處理、實(shí)時(shí)過濾和壓縮解壓縮等功能。例如,在圖像或視頻處理應(yīng)用中,F(xiàn)PGA可以對(duì)流入SDRAM的數(shù)據(jù)進(jìn)行邊緣檢測或格式轉(zhuǎn)換,減少后續(xù)處理負(fù)擔(dān)。利用FPGA的并行架構(gòu),可以實(shí)現(xiàn)多通道數(shù)據(jù)同時(shí)處理,提升系統(tǒng)整體性能。FPGA還可以與外部處理器(如CPU或DSP)協(xié)同工作,通過DMA(直接內(nèi)存訪問)機(jī)制實(shí)現(xiàn)高速數(shù)據(jù)傳輸,避免瓶頸問題。數(shù)據(jù)處理服務(wù)的設(shè)計(jì)需考慮資源優(yōu)化,例如使用流水線技術(shù)來平衡時(shí)序和面積開銷。

三、存儲(chǔ)支持服務(wù)

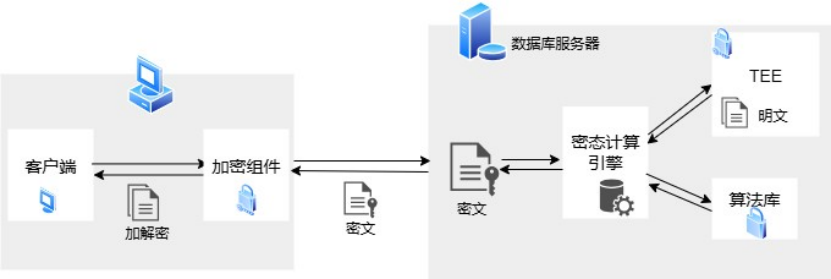

存儲(chǔ)支持服務(wù)涵蓋了數(shù)據(jù)持久化、備份和恢復(fù)機(jī)制。在FPGA實(shí)現(xiàn)中,可以通過邏輯控制實(shí)現(xiàn)數(shù)據(jù)分塊存儲(chǔ)和索引管理,支持快速檢索和更新。例如,為應(yīng)對(duì)SDRAM的易失性,可以設(shè)計(jì)非易失存儲(chǔ)接口(如Flash或SSD)的橋接模塊,實(shí)現(xiàn)數(shù)據(jù)自動(dòng)備份。同時(shí),F(xiàn)PGA能夠?qū)崿F(xiàn)存儲(chǔ)虛擬化,將多個(gè)SDRAM模塊組合為統(tǒng)一地址空間,提升存儲(chǔ)容量和帶寬。在嵌入式系統(tǒng)中,這些服務(wù)可擴(kuò)展為網(wǎng)絡(luò)存儲(chǔ)支持,通過以太網(wǎng)或PCIe接口提供遠(yuǎn)程數(shù)據(jù)訪問能力。安全方面,F(xiàn)PGA還可集成加密模塊,確保存儲(chǔ)數(shù)據(jù)的機(jī)密性和完整性。

四、實(shí)際應(yīng)用與優(yōu)化策略

在實(shí)際部署中,SDRAM文件結(jié)構(gòu)存儲(chǔ)控制的FPGA實(shí)現(xiàn)需綜合考慮功耗、時(shí)序和成本因素。優(yōu)化策略包括使用低功耗SDRAM型號(hào)、動(dòng)態(tài)頻率縮放以及基于FPGA的時(shí)鐘管理。通過仿真和時(shí)序分析,可以確保設(shè)計(jì)滿足嚴(yán)苛的時(shí)序要求。采用模塊化設(shè)計(jì)便于后期維護(hù)和升級(jí),例如通過IP核復(fù)用加速開發(fā)周期。隨著AI和物聯(lián)網(wǎng)的發(fā)展,這種FPGA實(shí)現(xiàn)在高性能計(jì)算和邊緣設(shè)備中具有廣闊前景,能夠?yàn)閺?fù)雜數(shù)據(jù)處理任務(wù)提供可靠的存儲(chǔ)基礎(chǔ)。

SDRAM文件結(jié)構(gòu)存儲(chǔ)控制的FPGA實(shí)現(xiàn)結(jié)合了硬件高效性和軟件靈活性,為現(xiàn)代數(shù)據(jù)處理系統(tǒng)提供了強(qiáng)大的支持服務(wù)。通過精心設(shè)計(jì)控制邏輯和集成數(shù)據(jù)處理功能,F(xiàn)PGA平臺(tái)能夠?qū)崿F(xiàn)高性能、低延遲的存儲(chǔ)解決方案,推動(dòng)數(shù)字技術(shù)的創(chuàng)新應(yīng)用。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.zeifo.cn/product/8.html

更新時(shí)間:2026-01-18 22:08:11